VLSI - Silicon on Insulator (SOI)

SOI Benefits:

- suppression of bottom junctions

- lower parasitic capacitance

- faster switching and/or lower power - full isolation

- no latch-up

- denser layout

- lower interferences between the analog and digital parts of a SoC

- lower losses in the passive components at high frequency

- lower leakage current , enabling operation at higher temperature (250°C)

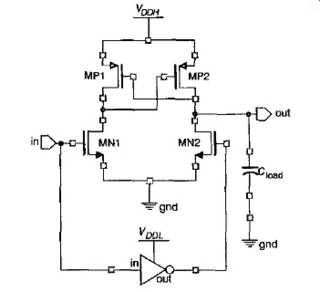

- but : floating body effect in partially-depleted transistors - thin active area

- lower sensitivity to radiations ( lower SEU sensitivity in memory cells )

Overall performance improvement (at same technology node):

- 25% faster

- 50% lower power consumption

- 10% smaller die size

From IBM white paper on SOI:

- One of the areas that can store charge in a MOS switch is the area between the impurities added to a chip’s silicon and the silicon substrate itself, which is free of impurities. That area is called the “junction capacitance”. If a thin layer of an insulator, such as glass, is placed between the impurities and the silicon substrate, the junction capacitance will be eliminated and the MOS transistor will operate faster.

- Even in cases where the quality of the SOI layer has been fine for making single chips or small circuits, the MOS transistor placed on the SOI layer has continued to pose serious challenges. When a MOS transistor is placed on SOI, it is also placed next to a parallel bipolar transistor. The bipolar transistor can turn on when the MOS switch passes current through itself, i.e. base current will be supplied through the base impact ionization.

- Dropping the voltage is very effective in reducing chip power. The ability of SOI as a low power source originates from the fact that SOI circuits can operate at low voltage with the same performance as a bulk technology at high voltage.

- As an example, measured on a 4 Mb SRAM. At the same performance as bulk CMOS, SOI can reduce the chip power by 1.7-3X (depending on the switching factor of the devices).